1. testbench

testbench是一种验证的手段。testbench就是对写的FPGA模块设计文件进行测试的文件。verilog和VHDL的国际标准里面有很多不能被综合实现的语句,比如initial,forever,repeat和延时语句等。但这些语句可以在模块仿真的时候使用。testbench的运行环境一般是ise或者vivado自带的仿真工具,或者如modelsim一样的第三方仿真工具。

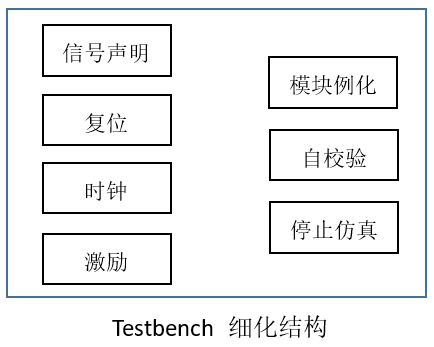

2. testbench组成

其中testbench最基本的结构包括信号声明、激励和模块例化,复位和时钟产生部分,也可以看做激励。根据设计的复杂度,需要引入时钟和复位部分。当然更为复杂的设计,激励部分也会更加复杂。根据自己的验证需求,选择是否需要自校验和停止仿真部分。

3.testbench模板

`timescale 1ns/1ps //时间精度

`define Clock 20 //时钟周期

module u_design_tb;

//==================<端口>==================================================

reg clk ; //时钟,50Mhz

reg rst_n ; //复位,低电平有效

reg [XX:0] in ; //

wire [XX:0] out ; //

//--------------------------------------------------------------------------

//-- 模块例化

//--------------------------------------------------------------------------

u_design u_design_inst

(

.clk (clk ),

.rst_n (rst_n ),

.in (in ),

.out (out )

);

//----------------------------------------------------------------------

//-- 时钟信号和复位信号

//----------------------------------------------------------------------

initial begin

clk = 0;

forever

#(`Clock/2) clk = ~clk;

end

initial begin

rst_n = 0; #(`Clock*20+1);

rst_n = 1;

end

//----------------------------------------------------------------------

//-- 设计输入信号

//----------------------------------------------------------------------

initial begin

in = 0;

#(`Clock*20+2); //初始化完成

$stop;

end

endmodule

4. testbench测试

`timescale 1ns / 1ps //时间精度

module fifo_wr_tb();

//==================<端口>==================================================

reg clk;

reg rst_n;

reg start_write;

reg start_send;

wire writing;

wire sending;

wire uart_txd;

//==================<模块例化>==================================================

fifo_top u_fifo_wr(

.sys_clk(clk),

.sys_rst_n(rst_n),

.key_0(start_write),

.key_1(start_send),

.led_0(writing),

.led_1(sending),

.uart_txd(uart_txd)

);

//==================<模块时钟>==================================================

initial clk = 1;

always #10 clk =!clk;

initial begin

rst_n = 0;

start_write = 1;

start_send = 1;

#201

rst_n = 1;

//==================<模块输入信号>==================================================

start_write = 0; //开始fifo写入

#30_000_000; //按键延时+去抖需要20ms以上

start_write = 1;

#10_000_000; //等待写入完毕

start_send = 0; //开始串口发送

#30_000_000; //按键延时+去抖需要20ms以上

start_send = 1;

#30_000_000;

$stop;

end

endmodule